16.11 Sincronizzazione

Nelle trasmissioni numeriche occorre ottenere allo stesso tempo sia la sincronizzazione della portante di demodulazione, nei limiti delle ambiguità di fase residue, sia la corretta temporizzazione di simbolo, per campionare le c.a. di b.f. ricevute al centro del periodo di simbolo, ed evitare l’insorgenza di isi. Le due problematiche possono essere affrontate l’una di seguito all’altra, adottando le soluzioni già esposte. D’altra parte sono ora possibili varianti, come ad esempio il Costas loop che, utilizzando entrambe le c.a. di b.f., realizza l’aggancio di frequenza anche per tecniche di modulazione a portante soppressa, oppure procedure che tentano di acquisire per primo il sincronismo di simbolo, e quindi usano i valori delle c.a. di b.f. ricevute per effettuare correzioni alla fase dell’oscillatore di demodulazione.

Qualora la portante di demodulazione presenti una ambiguità di fase residua si può applicare la tecnica della codifica differenziale esposta al §

16.4, oppure inserire una sequenza di simboli noti (o

flag) all’inizio della trama trasmissiva, in modo che il confronto tra i valori previsti e quelli ricevuti permetta di correggere tale ambiguità. Da notare che i

flag o

trailer ad inizio trama possono essere vantaggiosamente usati anche da schemi di recupero del clock del tipo di quelli al §

15.7.2.1.

16.11.1 Sincronizzazione per sistemi a spettro espanso

In questo caso occorre considerare anche la modalità di acquisizione della fase della sequenza pn necessaria al despreading, che avviene in due passi: il primo effettua una ricerca sequenziale ed ha una precisione di metà del periodo di chip Tp, mentre il secondo riduce l’errore mediante una tecnica a controreazione, e lo mantiene sotto controllo.

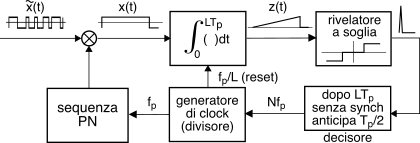

Considerando già avvenuta la sincronizzazione di portante e la demodulazione, il primo passo può essere attuato mediante lo schema in figura detto

sliding correlator, in cui l’integratore (ad es. un integrate and dump) calcola la correlazione tra la

pn in arrivo e quella generata localmente. In caso di coincidenza temporale il risultato

z(t) è una rampa (negativa se il bit fosse stato

− 1), mentre per un ritardo

θ tra la seq. locale e quella ricevuta il risultato dell’integrazione all’istante

LTp è l’autocorrelazione

Rx̃(θ), più termini di rumore a valor atteso nullo. Alla conclusione del periodo di bit

Tb = LTp il generatore di clock resetta l’integratore, non prima però che il rivelatore a soglia abbia prodotto un impulso di sincronismo, inibendo il componente di decisione e terminando la ricerca. In assenza di sincronizzazione, il decisore fa invece avanzare la fase della

pn di

Tp⁄2, tentando di nuovo l’aggancio. Il metodo richiede dunque

2L2Tp secondi (nel caso peggiore), tempo che può essere ridotto eseguendo più ricerche in parallelo.

Dopo aver acquisto la sincronizzazione

lasca il controllo della generazione della

pn passa ad un circuito indicato come

delay locked loop o

dll, che può essere realizzato in diversi modi, e di cui discutiamo il funzionamento dello schema

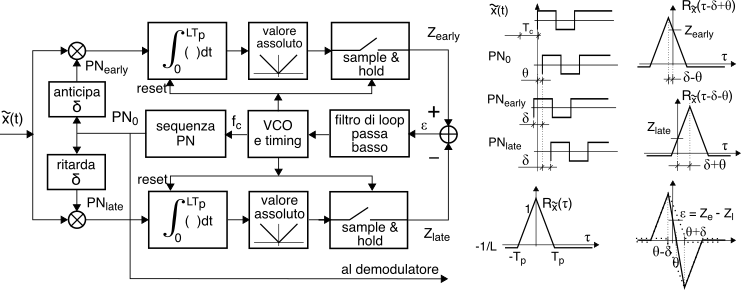

canonico mostrato in fig.

16.64.Un generatore pseudonoise produce la sequenza

pn0 affetta dall’errore di temporizzazione residuo

− Tp⁄2 ≤ |θ| ≤ Tp⁄2, che ai fini della discussione assumiamo come un ritardo, e dunque scriviamo

pn0 = x̃(t − θ); lo scopo del

dll è di rendere

θ = 0. Da

pn0 sono derivate due nuove sequenze,

pnearly = x̃(t − θ + δ) e

pnlate = x̃(t − θ − δ), che differiscono da

pn0 rispettivamente per un anticipo od un ritardo

δ < Tp⁄2, e che sono moltiplicate per il segnale allargato di banda base

x̃(t).

L’integratore del ramo superiore (

early) calcola pertanto l’autocorrelazione

Rx̃(δ − θ) = ∫LTp0 x̃(t) x̃(t − θ + δ) dt

tra

x̃(t) e la sua copia

in anticipo di

δ − θ, mentre quello inferiore (

late) calcola

Rx̃(− δ − θ) tra

x̃(t) e la sua copia

in ritardo di

δ + θ (vedi lato destro di fig.

16.64): questi due risultati sono campionati a fine sequenza, ed indicati con

zearly e

zlate; notiamo che se

θ = 0, si ha

zearly = zlate = Rx̃(δ).

Proseguendo con l’esempio, osserviamo come l’evenienza

zearly > zlate indichi che la fase di

pnearly è più prossima a quella del segnale ricevuto di quanto non lo sia quella di

pnlate, e dunque

pn0 è in ritardo, ovvero stiamo andando... troppo piano. In questo caso la differenza

ε = zearly − zlate risulta positiva (vedi costruzione grafica in basso a ds in fig.

16.64), e ciò determina (attraverso il filtro di loop) una

accelerazione del

vco, che tende quindi a ridurre il ritardo iniziale

θ. Se si fosse verificato l’opposto (

θ < 0 e dunque

zearly < zlate) sarebbe risultato

ε < 0, a cui corrisponde un

rallentamento del

vco.

Man mano che

θ si riduce,

pnearly e

pnlate tendono a disporsi simmetricamente in anticipo ed in ritardo di

δ rispetto a

pn0, in modo che

zearly e

zlate prendono il medesimo valore e la loro differenza

ε si annulla, la

fc prodotta dal

vco è costante, e

pn0 è esattamente in fase con

x̃(t). Mentre

θ si azzera, la costruzione grafica in basso a destra di fig.

16.64 transla verso sinistra, in modo che corrisponda

ε = 0 per

θ = 0. Ciò

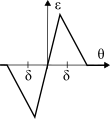

consente di riformulare l’approccio grafico come nella figura a lato, che rappresenta l’errore

ε in funzione del disallineamento

θ, detta anche

curva di discriminazione o

curva-s, e che evidenzia l’intervallo

|θ| < δ entro il quale il sistema converge. Questa figura è simile a quella discussa al §

12.2.2.2 a proposito del

pll, ed infatti l’analisi delle prestazioni ha molto in comune. In particolare una diminuzione della banda del filtro di loop, se da un lato riduce le capacità di inseguire rapide variazioni di ritardo (come potrebbe essere per effetto doppler), d’altro canto attenua l’influenza del rumore sulla varianza della stima di

θ.

Una alternativa possibile opera direttamente sul segnale modulato, e per questo indicata come dll incoerente, non necessitando della sincronizzazione di portante. Al posto dell’integratore utilizza un filtro passabanda centrato sulla portante, seguito da un demodulatore di inviluppo. Una ulteriore variante, indicata come tau-dither loop, affronta e risolve il problema legato ad un possibile diverso guadagno tra i due rami del dll.